cmos集成电路的阈值电压?

一、cmos集成电路的阈值电压?

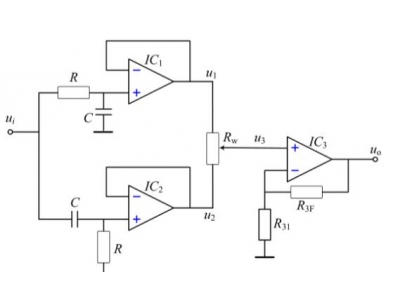

在数/模混合集成电路设计中电压基准是重要的模块之一。针对传统电路产生的基准电压易受电源电压和温度影响的缺点,提出一种新的设计方案,电路中不使用双极晶体管,利用PMOS和NMOS的阈值电压产生两个独立于电源电压和晶体管迁移率的负温度系数电压,通过将其相减抵消温度系数,从而得到任意大小的零温度系数基准电压值。该设计方案基于某公司0.5μm CMOS工艺设计,经HSpice仿真验证表明,各项指标均已达到设计要求。

电压基准是混合信号电路设计中一个非常重要的组成单元,它广泛应用于振荡器、锁相环、稳压器、ADC,DAC等电路中。产生基准的目的是建立一个与工艺和电源电压无关、不随温度变化的直流电压。目前最常见的实现方式是带隙(Bandgap)电压基准,它是利用一个正温度系数电压与一个负温度系数电压加权求和来获得零温度系数的基准电压。但是,在这种设计中,由于正温度系数的电压一般都是通过晶体管的be结压差得到的,负温度系数电压则直接利用晶体管的be 结电压。由于晶体管固有的温度特性使其具有以下局限性:

(1)CMOS工艺中对寄生晶体管的参数描述不十分明确;

(2)寄生晶体管基极接地的接法使其只能输出固定的电压;

(3)在整个温度区间内,由于Vbe和温度的非线性关系,当需要输出精确的基准电压时要进行相应的曲率补偿。

为了解决这些问题,提出一种基于CMOS阈值电压的基准设计方案。它巧妙利用PMOS和NMOS阈值电压的温度特性,合成产生与温度无关的电压基准,整个电路不使用双极晶体管,克服了非线性的温度因子,并能产生任意大小的基准电压值。

二、cmos反相器阈值电压的作用?

反相器电路输出电压所代表的逻辑电平与输入相反。反相器可以仅用一个NMOS晶体管或一个PMOS连接一个电阻来构建。因为这种“阻性漏极”方式只需要使用一种类型的晶体管,其制造成本非常小。不过,由于电流以两种状态之一流过电阻,这种阻性漏极配置有功耗和状态改变的处理速率问题。另外,反相器可以用两个互补晶体管配置成CMOS反相器。这种配置可以大幅降低功耗,因为在两种逻辑状态中,两个晶体管中的一个总是截止的。处理速率也能得到很好的提高,因为与NMOS型和PMOS型反相器相比,CMOS反相器的电阻相对较低。反相器也可以电阻-晶体管逻辑(RTL)或晶体管-晶体管逻辑(TTL)使用三极管(BJT)构建。

反相器性能常用表示输入-输出电压关系的电压传输特性曲线(VTC)来测定。曲线图能反映出元件的参数,包括噪声容限、增益和操作逻辑电平。

北卡罗来纳州立大学组建的20微米反相器的电压传输特性曲线

反相器理想化的电压传输特性曲线是单位阶跃函数,这表明反相器能在高电平和低电平间无延迟精确的翻转,但在实际元件中,曲线存在过渡区。曲线表明若输入为低电压,则输出为高电压;若输入为高电压,则输出电压逐渐接近0V。过渡区的斜率是性能测量的指标,过渡区越陡峭,即斜率越大,性能越好,若斜率接近无穷,则电路能在高电平和低电平间精确翻转,反相器就是理想的。

噪声容限可以通过每一工作区中的最大输出电压VOH和最小输入电压VIL的比值来测定。

输出电压VOH可以在级联多个元件时测定信号驱动强度。

三、cmos 宽长比与阈值电压公式?

CMOS反相器P管的宽长比比N管的大的原因是:这是和载流子有关,P管是空穴导电,N管电子导电,电子的迁移率大于空穴,同样的电场下,N管的电流大于P管,因此要增大P管的宽长比,使之对称,这样才能使得两者上升时间下降时间相等、高低电平的噪声容限一样、充电放电的时间相等。CMOS反相器的特点是:

(1) 静态功耗极低。在稳定时,CMOS反相器工作在工作区Ⅰ和工作区Ⅴ,总有一个MOS管处于截止状态,流过的电流为极小的漏电流。(2) 抗干扰能力较强。由于其阈值电平近似为0.5VDD,输入信号变化时,过渡变化陡峭,所以低电平噪声容限和高电平噪声容限近似相等,且随电源电压升高,抗干扰能力增强。(3) 电源利用率高。VOH=VDD,同时由于阈值电压随VDD变化而变化,所以允许VDD有较宽的变化范围,一般为+3~+18V。(4) 输入阻抗高,带负载能力强。

四、cmos管分类?

1、N沟道增强型 2、P沟道增强型 3、N沟道耗尽型 4、P沟道耗尽型

五、cmos管特点?

CMOS集成电路的特点有哪些?

CMOS集成电路功耗低

CMOS集成电路采用场效应管,且都是互补结构,工作时两个串联的场效应管总是处于一个管导通,另一个管截止的状态,电路静态功耗理论上为零。实际上,由于存在漏电流,CMOS电路尚有微量静态功耗。

CMOS集成电路工作电压范围宽

CMOS集成电路供电简单,供电电源体积小,基本上不需稳压。

CMOS集成电路逻辑摆幅大。

CMOS集成电路的逻辑高电平“1”、逻辑低电平“0”分别接近于电源高电位VDD及电影低电位VSS。因此,CMOS集成电路的电压电压利用系数在各类集成电路中指标是较高的。

CMOS集成电路抗干扰能力强。

CMOS集成电路的电压噪声容限的典型值为电源电压的45%,保证值为电源电压的30%。随着电源电压的增加,噪声容限电压的绝对值将成比例增加。

CMOS集成电路输入阻抗高。

CMOS集成电路的输入端一般都是由保护二极管和串联电阻构成的保护网络,故比一般场效应管的输入电阻稍小,但在正常工作电压范围内,这些保护二极管均处于反向偏置状态,直流输入阻抗取决于这些二极管的泄露电流,通常情况下,等效输入阻抗高达103~1011Ω,因此CMOS集成电路几乎不消耗驱动电路的功率。

CMOS集成电路温度稳定性能好。

由于CMOS集成电路的功耗很低,内部发热量少,而且,CMOS电路线路结构和电气参数都具有对称性,在温度环境发生变化时,某些参数能起到自动补偿作用,因而CMOS集成电路的温度特性非常好。

CMOS集成电路扇出能力强。

扇出能力是用电路输出端所能带动的输入端数来表示的。由于CMOS集成电路的输入阻抗极高,因此电路的输出能力受输入电容的限制,但是,当CMOS集成电路用来驱动同类型,如不考虑速度,一般可以驱动50个以上的输入端。

CMOS集成电路抗辐射能力强。

CMOS集成电路中的基本器件是MOS晶体管,属于多数载流子导电器件。各种射线、辐射对其导电性能的影响都有限,因而特别适用于制作航天及核实验设备。

CMOS集成电路可控性好

CMOS集成电路输出波形的上升和下降时间可以控制,其输出的上升和下降时间的典型值为电路传输延迟时间的125%~140%。

CMOS集成电路接口方便

因为CMOS集成电路的输入阻抗高和输出摆幅大,所以易于被其他电路所驱动,也容易驱动其他类型的电路或器件。

六、mos管为什么有阈值电压?

阈值电压(Threshold voltage)

通常将传输特性曲线中输出电流随输入电压改变而急剧变化转折区的中点对应的输入电压称为阈值电压。

MOS管,当器件由耗尽向反型转变时,要经历一个 Si 表面电子浓度等于空穴浓度的状态。此时器 件处于临界导通状态,器件的栅电压定义为阈值电压,它是MOSFET的重要参数之一 。

七、cmos晶体管原理?

cmos晶体管又称场效应管,即在集成电路中绝缘性场效应管。

该管原理为导通时只有一种极性的载流子(多子)参与导电,是单极型晶体管。导电机理与小功率MOS管相同,但结构上有较大区别,小功率MOS管是横向导电器件,功率MOSFET大都采用垂直导电结构,又称为VMOSFET,大大提高了MOSFET器件的耐压和耐电流能力。

八、二极管阈值电压怎么求?

二极管的正向两端电压降不是0。一般小功率二极管的正向两端电压降是0.7V,阈值0.5V,电压由0增加过阈值0.5V后,很快就稳定在0.7V。

阈值电压:指电压的临界点。例如,硅二极管的正向阈值电压为0.7V,当二极管的正向功率低于阈值电压时,二极管将停止工作,并进入截止状态。可以说0.7V是硅二极管的阈值电压。阈值电压广泛应用于工业控制、逆变器、家用电器等领域。最常见的是手机充电器。阈值电压为4.2V。当电池达到4.2V时,它将进入另一个状态。

九、cmos管怎么判断逻辑功能?

TTL门电路的输入端悬空时相当于高电平输入输入端接有电阻时其电阻阻值大于1.4K时该端也相当于高电平电阻值小于0.8K时该端才是低电平。 而CMOS逻辑门电路输入端不管是接大电阻还是接小电阻该端都相当于低电平即地电位。按照这个原则判断很清晰了

十、芯片底层都是cmos管吗?

现在的IC都是CMOS工艺,功耗及低,即IC里面全是MOS开关管,这应该是最底层的。

CMOS工艺是在PMOS和NMOS工艺基础上发展起来的。CMOS中的C表示“互补”,即将NMOS器件和PMOS器件同时制作在同一硅衬底上,制作CMOS集成电路。

CMOS集成电路具有功耗低、速度快、抗干扰能力强、集成度高等众多优点。CMOS工艺目前已成为当前大规模集 成电路的主流工艺技术,绝大部分集成电路都是用CMOS工艺制造的。

推荐阅读