vhdl与汇编语言的区别?

一、vhdl与汇编语言的区别?

除了应用领域、抽象级别、代码结构、可移植性和开发环境之外,VHDL和汇编语言在其他方面也存在一些区别。以下是一些额外的角度来比较它们:

1. 设计目标:VHDL的设计目标是描述硬件行为和功能,以便进行电路设计、仿真和验证。它强调的是电路的结构和行为,以及如何实现特定的功能。而汇编语言的设计目标是直接控制计算机硬件,以执行特定的指令序列。

2. 抽象层次:VHDL操作更高层次的抽象,可以描述逻辑门级别、寄存器传输级别(RTL)甚至系统级别的电路。它允许工程师使用高级概念来描述电路功能,并且具有模块化和层次化结构。而汇编语言操作更低层次的抽象,直接与处理器指令和寄存器进行交互。

3. 可读性:VHDL是一种结构化、可读性较高的语言,通过使用模块化结构和丰富的语法来提高代码可读性。相比之下,汇编语言通常更加底层,代码更加紧凑且难以理解,需要对底层硬件有深入的了解。

4. 软硬件交互:VHDL主要用于硬件设计和开发,与其他硬件描述语言(如Verilog)结合使用,可以进行综合、布局和布线等步骤,生成实际的电路。而汇编语言通常与高级编程语言(如C或C++)结合使用,可以编写底层的驱动程序、操作系统内核等软件部分。

5. 系统复杂性:由于VHDL主要用于描述和设计复杂的数字电路,它通常用于处理较大规模、高度并行的系统。相比之下,汇编语言更适用于对计算机底层进行细粒度控制和优化的场景。

这些是VHDL和汇编语言在不同角度上的一些区别。请注意,每种语言都有其特定的应用领域和优势,并且选择使用哪种语言取决于具体的需求和目标。

二、vhdl进行数字逻辑设计的前提是什么?

vhdl进行数字逻辑设计的前提是运用正常。内容是应用数字电路进行,数字系统逻辑设计。电子数字计算机是由具有各种逻辑功能的逻辑部件组成的,这些逻辑部件按其结构可分为组合逻辑电路和时序逻辑电路。组合逻辑电路是由 与门、 或门和非门等门电路组合形成的逻辑电路。

三、逻辑芯片与数字芯片区别?

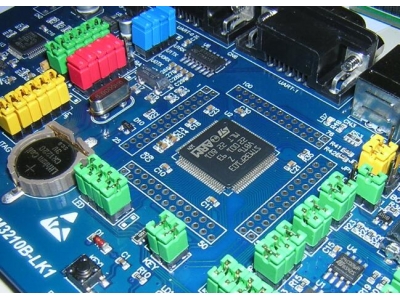

逻辑芯片又叫可编程逻辑器件,英文全称为:programmable logic device 即 PLD。PLD是做为一种通用集成电路产生的,他的逻辑功能按照用户对器件编程来确定。一般的PLD的集成度很高,足以满足设计一般的数字系统的需要。 PLD与一般数字芯片不同的是:PLD内部的数字电路可以在出厂后才规划决定,有些类型的PLD也允许在规划决定后再次进行变更、改变,而一般数字芯片在出厂前就已经决定其内部电路,无法在出厂后再次改变。

四、计算机硬件描述语言(VHDL)与编程语言(C语言)的区别及关系?

首先说VHDL:它是描述电路的计算机工具,早期的CPLD等器件是基于与-或阵列的,更容易说明这点,VHDL是描述电路行为的,当下载到器件后,它就是具体的电路,这个电路全由与-或阵列组成。后期的FPGA也一样,只是它是基于查找表的。再说C语言:我们可以认为它是用于控制特定电路的工作。我们都知道可以C编程的控制器都有程序存储器,它里面就存放了C编译后的二进制代码。而VHDL里下载后根本就不需要这个存放程序的地方。

五、计算机硬件描述语言(VHDL)与编程语言(C语言)的区别及关系?

做单片机方面,汇编语言是必学的,虽然单片机编程所用的大部分是C语言!VhdL语言是针对FPGA和CPLD的硬件描述语言,两者没多大共同点,是针对两个不同领域的语言!学习单片机后,你可以往ARM和DSP方向发展!现在电子的一个大方向你也可以单独学习VHDL,将FPGA学懂,那么你就是兼顾电子两大类的最尖端人才了!

六、c语言逻辑与或非用什么表示?

C语言中的与、或、非是C语言的逻辑运算符。

1、逻辑与在C语言中逻辑与用&&表示;

2、逻辑或在C语言中逻辑或用||表示;

3、逻辑非在C语言中逻辑非用!表示。

三种逻辑运算符中,逻辑非 ! 的优先级最高,逻辑与 && 次之,逻辑或 || 优先级最低。即算术、逻辑、赋值运算符的优先级顺序为:

逻辑非 ! >算术 > 逻辑与 &&、逻辑或 || > 赋值=

七、c语言中逻辑与运算的法则?

在 C 语言中,逻辑与运算符是 && ,它的运算规则如下:

如果第一个操作数为 true (非零值),则逻辑与运算符会对第二个操作数进行求值,并返回第二个操作数的值。

如果第一个操作数为 false (零值),则逻辑与运算符会立即返回 false ,不会对第二个操作数进行求值。

换句话说,逻辑与运算符会检查两个操作数是否同时为 true ,如果是,则返回 true ,否则返回 false 。

例如,如果你有以下两个表达式:

a = 5;

b = 3;

那么 a > 4 && b == 3 的结果为 true ,因为 a 确实大于 4,并且 b 确实等于 3。

但是,如果你将 b 改为 4,那么结果就变成了 false ,因为 a 仍然大于 4,但 b 不等于 3。

需要注意的是,逻辑与运算符的优先级低于逻辑或运算符(

),但高于逻辑非运算符(!)。如果需要改变运算顺序,可以使用括号来指定优先级。

八、基于vhdl语言的8位数字频率计的设计?

实验目的: 设计一个4位十进制频率计,学习复杂数字系统的设计方法。实验原理:根据频率的定义和频率测量的基本原理,测定信号的频率必须有一个脉宽为1秒的脉冲计数允许信号,1秒计数结束后,计数值(即所测信号频率)锁入锁存器,并为下一次测频作准备,即将计数器清零。试验内容:1、根据频率计的工作原理,将电路划分成控制器、计数器、锁存器和LED显示几个模块, 控制器――产生1秒脉宽的计数允许信号、锁存信号和计数器清零信号计数器――对输入信号的脉冲数进行累计锁存器――锁存测得的频率值LED显示――将频率值显示在数码管上顶层文件框图如下: 2、用元件例化语句写出频率计的顶层文件。提示:十进制计数器输出的应是4位十进制数的BCD码,因此输出一共是4×4bit。实验结果:各模块电路的VHDL描述:10进制计数器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt10 is port (rst,fx,ena:in std_logic; cout: out std_logic; outy :out std_logic_vector(3 downto 0));end cnt10;architecture behv of cnt10 isbegin process (rst,ena,fx) variable cqi :std_logic_vector(3 downto 0);begin if rst='1' then cqi :=(others =>'0'); elsif fx'event and fx='1' then if ena ='1' then if cqi < 9 then cqi:=cqi+1;cout<='0'; elsif cqi=9 then cqi :=(others =>'0'); cout<='1'; end if; elsif ena='0' then cqi:=(others =>'0'); end if;end if; outy <=cqi;end process;end behv;4位10进计数器library ieee;use ieee.std_logic_1164.all;entity cnt10_4 isport(fx,rst,ena:in std_logic; d:out std_logic_vector(15 downto 0));end entity;architecture one of cnt10_4 iscomponent cnt10 port (rst,fx,ena:in std_logic; cout: out std_logic; outy :out std_logic_vector(3 downto 0));end component;signal e:std_logic_vector(3 downto 0);beginu1:cnt10 port map(fx=>fx,rst=>rst,ena=>ena,cout=>e(0),outy=>d(3 downto 0));u2:cnt10 port map(fx=>e(0),rst=>rst,ena=>ena,cout=>e(1),outy=>d(7 downto 4));u3:cnt10 port map(fx=>e(1),rst=>rst,ena=>ena,cout=>e(2),outy=>d(11 downto 8));u4:cnt10 port map(fx=>e(2),rst=>rst,ena=>ena,cout=>e(3),outy=>d(15 downto 12));end architecture one;16位锁存器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity latch4 isport(d:in std_logic_vector(15 downto 0);ena,clk:in std_logic;q:out std_logic_vector(15 downto 0));end latch4;architecture one of latch4 isbeginprocess(clk,ena,d)variable cqi:std_logic_vector(15 downto 0);beginif ena='0' then cqi:=cqi;elsif clk'event and clk='1' then cqi:=d;end if;q<=cqi;end process;end one;LED控制模块library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity led_controller isport(d:in std_logic_vector(3 downto 0);a:out std_logic_vector(6 downto 0));end led_controller;architecture one of led_controller isbegin process(d)begincase d iswhen "0000"=> a<="0111111";when "0001"=> a<="0000110";when "0010"=> a<="1011011";when "0011"=> a<="1001111";when "0100"=> a<="1100110";when "0101"=> a<="1101101";when "0110"=> a<="1111101";when "0111"=> a<="0000111";when "1000"=> a<="1111111";when "1001"=> a<="1101111";when "1010"=> a<="1110111";when "1011"=> a<="1111100";when "1100"=> a<="0111001";when "1101"=> a<="1011110";when "1110"=> a<="1111001";when "1111"=> a<="1110001";when others=> null;end case;end process;end;控制模块library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity control is port (clk:in std_logic; rst,ena: out std_logic);end control;architecture behv of control isbegin process (clk) variable cqi :std_logic_vector(2 downto 0);begin if clk'event and clk='1' then if cqi <1 then cqi:=cqi+1;ena<='1';rst<='0'; elsif cqi=1 then cqi :=(others =>'0'); ena<='0';rst<='1'; end if; end if; end process;end behv;总体例化语句:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cntf isport(rset,clk:in std_logic; fx:in std_logic; ledout:out std_logic_vector(27 downto 0));end entity;architecture one of cntf iscomponent control port (clk:in std_logic; rst,ena: out std_logic);end component;component cnt10_4port(fx,rst,ena:in std_logic; d:out std_logic_vector(15 downto 0));end component;component latch4port(d:in std_logic_vector(15 downto 0);ena,clk:in std_logic;q:out std_logic_vector(15 downto 0));end component;component led_controllerport(d:in std_logic_vector(3 downto 0);a:out std_logic_vector(6 downto 0));end component;signal x,z:std_logic;signal g,h:std_logic_vector(15 downto 0);signal leds:std_logic_vector(27 downto 0);beginu1: control port map(clk=>clk,ena=>x,rst=>z);u2: cnt10_4 port map(fx=>fx,rst=>z,ena=>x,d=>g);u3: latch4 port map(clk=>clk,ena=>x,d=>g,q=>h);u4: led_controller port map(d(3 downto 0)=>h(3 downto 0),a(6 downto 0)=>leds(6 downto 0));u5: led_controller port map(d(3 downto 0)=>h(7 downto 4),a(6 downto 0)=>leds(13 downto 7));u6: led_controller port map(d(3 downto 0)=>h(11 downto 8),a(6 downto 0)=>leds(20 downto 14));u7: led_controller port map(d(3 downto 0)=>h(15 downto 12),a(6 downto 0)=>leds(27 downto 21));ledout<=leds;end; 这是我当时做的一个4位频率计,CLK为一个1HZ的时钟信号。可用数码管显示出频率数的。只要你能读懂原理,是很容易改成八位的。 如果要图文混合设计,即各模块设计好后,顶层文件用原理图设计即可。给你参考一下吧。

九、数字电路设计中,不同逻辑电平接口设计需要考虑哪些因素?

首先应该考虑不同逻辑电平之间是否需要隔离,是否共地。

其次在设计时要详细参阅各个逻辑芯片的资料,以确定相连接的芯片间逻辑电平输出与输入的电压值是否可以兼容,最好不要恰好在临界值,会导致系统不稳定。各芯片的输出端口电流驱动能力,是否可以满足需要?十、数字电路与数字逻辑和信号与系统哪个更有用?

本人就是学这的,来给你解答。

这2门是所有相关专业都必须学的。相比较而言,数字电路是基础中的基础,而信号与系统,偏向于系统。数字电路必须学好,知识必须要牢固。信号与系统也重要,其中的很多思想你要理解,知识不一定非得全部记住。应聘的时候数字电路知识考得多,问的也多。