判奇电路原理?

一、判奇电路原理?

判奇电路多见于电路结构中,其作用十分广泛,有一定的选择作用。

判奇电路一种简单的情况就是多数表决电路。

比如判断一个运动员的成绩是否有效,可以设3个裁判,给出一定的判决条件,如:主裁判和至少一名副裁判判断合格就合格。

判奇电路用数字电路实现。

判奇电路原理:

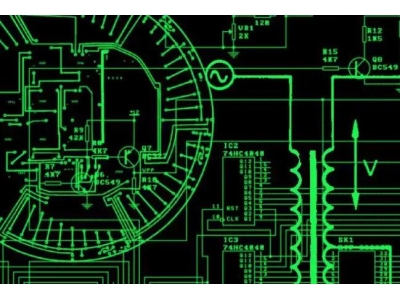

由于需要较高的判决灵敏度,所以比较器采用共源共栅差分电路形式,这种电路形式具有较高的电路增益。

VIN 为输入信号,VREF 为参考电压即电路的门限电压,VDD 为电源,VCC 为共源共栅差分电路的偏置电压。

锁存器采用"型D 触发器(使用双时钟),它比使用单时钟的I型触发器的工作频率要高一倍,VCLKl 和VCLK2 为时钟输入,控制锁存器锁存与否,VOl 和VO2 为整个电路的输出。

电路的每一级输出均采用源跟随器形式,起电平移位及增强驱动能力的作用。

由于电路是差分工作形式,所以VCLKl、VCLK2 为互补时钟信号。

二、判奇电路表达式?

当输入的三个变量A、B、C中1的个数为奇数时,输出为1;否则为0。F=A'B'C+A'BC'+AB'C'+ABC (A'表示A非)。

(1)判奇电路。输入中有奇数个1时,输出为1,否则为0。

(2)判偶电路。输入中有偶数个1时,输出为1,否则为0。

(3)判一致电路。输入变量取值相同时,输出为1,否则为0。

(4)判不一致电路。输入变量取值不一致时,输出为1,否则为0。

三、三变量判奇电路讲解?

三变量的判偶,意思是要判断其中是否只有两个变量的值相等,仅此而已。

与判偶相对,排除只有两个变量的值相等(=1)的就是了,应该说,在逻辑电路上,偶数是个实际数,0个输入是不能算作偶数的。

列真值表,设输入ABC三个端钮,输出Y,把三变量的八种取值全部罗列,偶数个意识,Y为1,其他为零。根据真值表列表达式,用与非门实现需要对表达式取非,再利用摩根定律将与或关系变换成与非即可。

扩展资料

逻辑电路一般有几个输入端和一个或几个输出端,当输入信号满足特定的逻辑关系时,电路开路,就有输出;否则,电路是闭合的,没有输出。

内容主要包括数字电子技术(几种逻辑电路)、门电路基础(半导体特性的分立元件、TTL集成电路CMOS集成电路)、组合逻辑电路(加法器、编码器和解码器集成逻辑功能)、时序逻辑电路(计数器、寄存器)、以及d/a和模数转换。

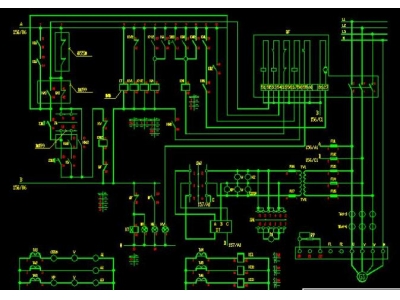

四、利用与非门设计三变量的判奇电路?

解:设输入三变量A、B、C,输出Y则:

1、真值表

A B C Y

0 0 0 0

0 0 1 1

0 1 0 1

0 1 1 0

1 0 0 1

1 0 1 0

1 1 0 0

1 1 1 1

2、逻辑表达式

Y=ABC+AB'C'+A'BC'+A'B'C

3、卡诺图

C\AB 00 01 10 11

0 0 1 1 0

1 1 0 0 1

4、逻辑图(略),可按下面表达式画图。三个反相器,4个三输入与非门,一个四输入与非门。

Y=[(ABC)'(AB'C')'(A'BC')'(A'B'C)]'

五、试用门电路设计一个三变量判奇电路?

当输入的三个变量A、B、C中1的个数为奇数时,输出为1;否则为0。

1、真值表

2、逻辑表达式

F=A'B'C+A'BC'+AB'C'+ABC (A'表示A非)

六、万秀奇判多少年?

没有判刑。

万秀奇,男,汉族,1963年11月出生,江西九江人,1981年10月参加工作,1983年9月加入中国共产党,解放军电子工程学院雷达技术专业毕业,中央党校在职大学学历。

七、三变量的判偶逻辑电路?

第一步:三个变量每次输入相加求和,第二步:所求的和除二,第三步:整除的判为1(偶数),有小数的判为0(奇数)。

八、奇骏can通讯电路故障?

1.可能有短路,断路,对地。

解决方法:首先是排查一下线路有没有出现短路,有没有对地或者是对电源这边出现断路的现象,如果有的就需要检查一下接头,还有线路这边及时进行维修。注意测量一下CAN线的电压和电阻。

2.测量发动机模块的电阻。

解决方法:测量下针脚6和14的电阻是60欧姆还是120欧姆。如果是120欧姆表示发动机模块损坏。这时候就需要更换发动机的模块。

3.也可能系统的通讯故障。

解决方法:如果所有的模块都不能通讯的话,排除模块和线路的问题,也有可能是系统这边出现问题,需要重新进行升级之后才可以使用。

九、海丰马小奇判多少年?

无法确定具体年数。因为海丰马小奇是一个虚构的人物,不存在实际的判刑情况。如果你指的是某个真实的案例中的被告人,需要提供更多的具体信息,如名字、犯罪事实、法院判决等,才能进行判决年数的计算。内容延伸:在实际的法律判决中,刑期的长短通常由犯罪的性质、犯罪的情节、被告人的认罪态度、是否具有立功表现等因素决定。同时,不同国家和地区的法律制度也可能存在差异。因此,在对任何一个案件做出准确的判决年数估计前,要充分考虑上述多种因素。

十、什么叫三变量判一致电路?

第一:三个变量每次输入相加求

第二:所求的和除二,

第三:整除的判为1(偶数),有小数的判为0(奇数)。

用一个电路实现对之前的一个计数器里面所记的数是奇数或是偶数的的判定。

列真值表,设输入ABC三个端钮,输出Y,把三变量的八种取值全部罗列,偶数个一时,Y为1,其他为零。根据真值表列表达式,用与非门实现需要对表达式取非,再利用摩根定律将与或关系变换成与非即可。

扩展资料:

任何时刻输出信号的逻辑状态仅取决于该时刻输入信号的逻辑状态,而与输入信号和输出信号过去状态无关的逻辑电路。由于组合逻辑电路的输出逻辑状态与电路的历史情况无关,所以它的电路中不包含记忆性电路或器件。

门电路,组合逻辑电路的基本单元。当前组合逻辑电路都已制成标准化、系列化的中、大规模集成电路可供选用。