cpld基本知识?

一、cpld基本知识?

CPLD(Complex Programmable Logic Device)是Complex PLD的简称,一种较PLD为复杂的逻辑元件。

20世纪70年代,最早的可编程逻辑器件--PLD诞生了。其输出结构是可编程的逻辑宏单元,因为它的硬件结构设计可由软件完成(相当于房子盖好后人工设计局部室内结构),因而它的设计比纯硬件的数字电路具有很强的灵活性,但其过于简单的结构也使它们只能实现规模较小的电路。为弥补PLD只能设计小规模电路这一缺陷,20世纪80年代中期,推出了复杂可编程逻辑器件--CPLD。目前应用已深入网络、仪器仪表、汽车电子、数控机床、航天测控设备等方面。

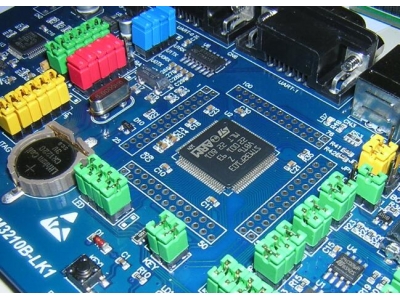

二、cpld芯片

什么是CPLD芯片?

CPLD芯片,全称复杂可编程逻辑器件(Complex Programmable Logic Device),是一种集成电路芯片,用于实现数字逻辑电路的可编程功能。它是数字电子系统中的核心构件之一,广泛应用于各种电子设备和嵌入式系统中。CPLD芯片以其灵活性、可编程性和高效性而备受青睐,成为现代电子行业中不可或缺的组成部分。

CPLD芯片由一系列可编程逻辑单元(Programmable Logic Elements, PLE)组成,这些单元通常包含逻辑门、触发器和存储器单元。通过编程,可以根据实际需求来配置这些逻辑单元,从而实现各种各样的数字逻辑功能。

CPLD芯片的优势

相比于传统的固定功能集成电路,CPLD芯片具有许多显著的优势:

- 灵活性:通过编程,CPLD芯片可以适应多种不同的应用需求,而不需要重新设计、制造和测试定制的专用电路。

- 可重构性:CPLD芯片的逻辑功能可以被修改和更新,以适应不同阶段的产品需求变化,从而提高产品的灵活性和可维护性。

- 可编程性:CPLD芯片可以通过硬件描述语言(HDL)或图形编程界面进行编程,使得设计人员可以快速而轻松地实现复杂的数字逻辑功能。

- 集成度高:CPLD芯片集成了大量的逻辑单元,可以实现复杂的逻辑功能,并且占用较少的空间。

- 功耗低:相比于其他可编程逻辑器件,CPLD芯片通常具有较低的功耗,有助于提高系统的能效。

CPLD芯片的应用领域

CPLD芯片在各种领域都有广泛的应用:

- 通信:在通信系统中,CPLD芯片可以实现高速数据处理、通信协议处理、时序控制等功能,提高系统性能和可靠性。

- 工业自动化:在工业自动化领域,CPLD芯片可以用于控制系统、数据采集和信号处理等应用,实现精确控制和高效运行。

- 嵌入式系统:CPLD芯片可以嵌入到各种嵌入式系统中,例如数字电视、智能手机、汽车电子等,提供灵活的逻辑功能和高性能的数据处理。

- 医疗设备:在医疗设备中,CPLD芯片可以用于实现各种实时监测、信号处理和控制功能,提高设备的准确性和稳定性。

- 航空航天:在航空航天领域,CPLD芯片广泛应用于飞控系统、导航系统和通信系统等,保证航天器的安全和可靠性。

CPLD芯片的未来发展

随着科技的不断进步,CPLD芯片在未来会继续得到广泛应用和发展。

首先,随着物联网和人工智能的兴起,对数字逻辑处理能力的需求将会越来越大。CPLD芯片作为一种高性能、可编程的器件,将在物联网设备和人工智能系统中发挥重要作用。

其次,随着制造工艺的不断改进和集成度的提高,CPLD芯片将越来越小型化、高集成化,提供更高性能的数字逻辑处理功能。

此外,CPLD芯片的功耗和能效也将得到更多关注和改进,以满足节能环保的需求。

综上所述,CPLD芯片作为一种灵活可编程的逻辑器件,具有广泛的应用前景和发展空间。在未来的数字化时代,CPLD芯片将继续发挥其独特优势,推动数字电子技术的不断革新和进步。

三、基本逻辑电路叫什么门?

基本逻辑门电路有与门、或门、非门和与非门,其中最常用的基本逻辑门电路是与非门。

四、plc基本逻辑电路有哪些?

逻辑电路是一种离散信号的传递和处理,以二进制为原理、实现数字信号逻辑运算和操作的电路。分组合逻辑电路和时序逻辑电路。

前者由最基本的“与门”电路、“或门”电路和“非门”电路组成,其输出值仅依赖于其输入变量的当前值,与输入变量的过去值无关—即不具记忆和存储功能。

五、cpld的发展

标题:CPLD的发展历程

CPLD作为一种先进的可编程芯片,近年来在嵌入式系统开发领域得到了广泛的应用。作为一种高度集成的芯片,CPLD的发展历程可以追溯到上世纪80年代,经过几十年的发展,其性能和功能得到了不断的提升和优化。在过去的几十年中,CPLD经历了几个重要的阶段。最初,CPLD的设计主要基于硬件描述语言,如VHDL和Verilog。随着技术的发展,CPLD的设计语言逐渐变得更加灵活和多样化,如基于C语言的开发环境也逐渐得到了广泛的应用。同时,CPLD的编程方式也从传统的串行编程发展到了并行编程,大大提高了开发效率。

随着嵌入式系统的不断发展,CPLD的应用范围也越来越广泛。从简单的数字逻辑到复杂的控制系统,CPLD都发挥着重要的作用。同时,随着物联网、人工智能等新兴技术的发展,CPLD的应用场景也在不断拓展,其未来的发展前景非常广阔。

关键字:cpld的发展

六、三大基本逻辑电路是指?

1.非门:

利用内部结构,使输入的电平变成相反的电平,高电平(1)变低电平(0),低电平(0)变高电平(1)。

2.与门:

利用内部结构,使输入两个高电平(1),输出高电平(1),不满足有两个高电平(1)则输出低电平(0)。

3.或门:

利用内部结构,使输入至少一个输入高电平(1),输出高电平(1),不满足有两个低电(0)输出高电平(1)

七、基本逻辑电路分析与设计的区别?

分析是研究分析电路设计是按电路设计应用的线路

八、简述分析组合逻辑电路的基本步骤?

分析组合逻辑电路的基本步骤:一 、首先掌握各种逻辑部件功能。二 、从输出部分查看需要达到目的。三 、然后从输出电路向前推每一层电路功能分析输入信号的逻辑变化过程。

九、数字逻辑电路的基本原理?

模拟电路处理的信号电压变化是连续的,比如正弦波信号。数字电路处理的信号只有高电平和低电平,是数字脉冲信号。一般用高电平代表“1” ,低电平代表“0”,用二进制数字的运算来表示各种逻辑关系。

十、组合逻辑电路的基本单元是什么?'?

组合逻辑电路的基本单元是由“与”、“或”、“非”三种门电路组成 。

“门”是这样的一种电路:它规定各个输入信号之间满足某种逻辑关系时,才有信号输出,通常有下列三种门电路:与门、或门、非门(反相器)。

从逻辑关系看,门电路的输入端或输出端只有两种状态,无信号以“0”表示,有信号以“1”表示。也可以这样规定:低电平为“0”,高电平为“1”,称为正逻辑。

反之,如果规定高电平为“0”,低电平为“1”称为负逻辑,然而,高与低是相对的,所以在实际电路中要先说明采用什么逻辑,才有实际意义;

例如,负与门对“1”来说,具有“与”的关系,但对“0”来说,却有“或”的关系,即负与门也就是正或门;同理,负或门对“1”来说,具有“或”的关系,但对“0”来说具有“与”的关系,即负或门也就是正与门